Analyse, Verifikation und Optimierung des Einkapselungsprozesses von Mikrochips

EXPERTEN-TIPP

Der Trend zur Intellektualisierung und der Wunsch nach Elektrofahrzeugen erzeugt einen steigenden Bedarf an zuverlässigen, leistungsfähigen IC-Produktleistung in der globalen Industrie. Eine fortschrittliche IC-Packaging-Technologie ist dabei unerlässlich und spielt eine zunehmend wichtigere Rolle im Herstellungsprozess.

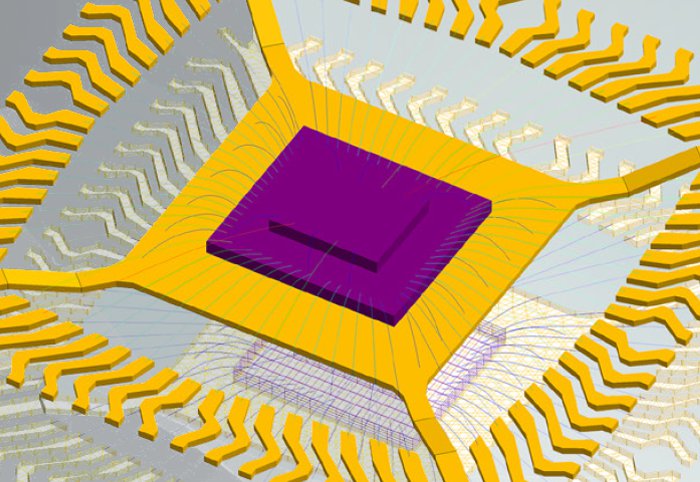

IC Package ermöglicht eine vollständige und umfassende Analyse, Verifikation und Optimierung des Einkapselungsprozesses von Mikrochips. Der 3D-Solver analysiert das Füllen, die Aushärtung, den Verzug und die Verformung der Leiterdrähte durch das einströmende Material. Die genauen Ergebnisse helfen den Einkapselungsprozess detailliert zu analysieren und sowohl den Prozess als auch das Design des Bauteils zu optimieren.

Plastic Chip Encapsulation ist ein Spritzgussverfahren, bei dem Chips mit Epoxy Molding Compound (EMC) verkapselt werden, um physikalische Schäden oder Korrosion zu vermeiden. Abgebildet werden Interaktionen zwischen Mikrochips und anderen Elektronikkomponenten, der Aushärtungsprozess des duroplastischen Materials sowie verschiedene Einflussfaktoren auf die Prozessbedingungen.

Die Komplexität und die Herausforderung bei der Simulation des Chip-Verkapselungsprozess liegt in der Verschiedenartigkeit der einzelnen Materialkomponenten, wie z. B. EMC, Chip, Leadframe oder Drahtdichte usw. begründet. Häufige Defekte sind unvollständige Füllungen, Schweißnähte, Lufteinschlüsse, Hohlräume, Wire Sweep, Paddel Shift, Risse und Verzüge, usw..

Gern beantworten wir Ihre Fragen und informieren Sie im Detail über IC-Packaging. Bitte wenden Sie sich an: 0241 565 276-0 oder senden Sie eine Email an sales@simpatec.com .